Nmos inverter with resister load ¾if v i nmos inverter</strong> with resister load saturation region Nmos inverter l13 cmos inverter. For an ideal symmetric transistor, (w/l) ratio of pmos transistor is approximately 2.5 times (w/l) ratio of nmos transistor to compensate the driving current loss in pmos transistor due to lower hole mobility.

Nmos Inverter

Nmos inverter m1 m2 m3 x v out v in figure 1.

The two nmos transistors are defined is different ways.

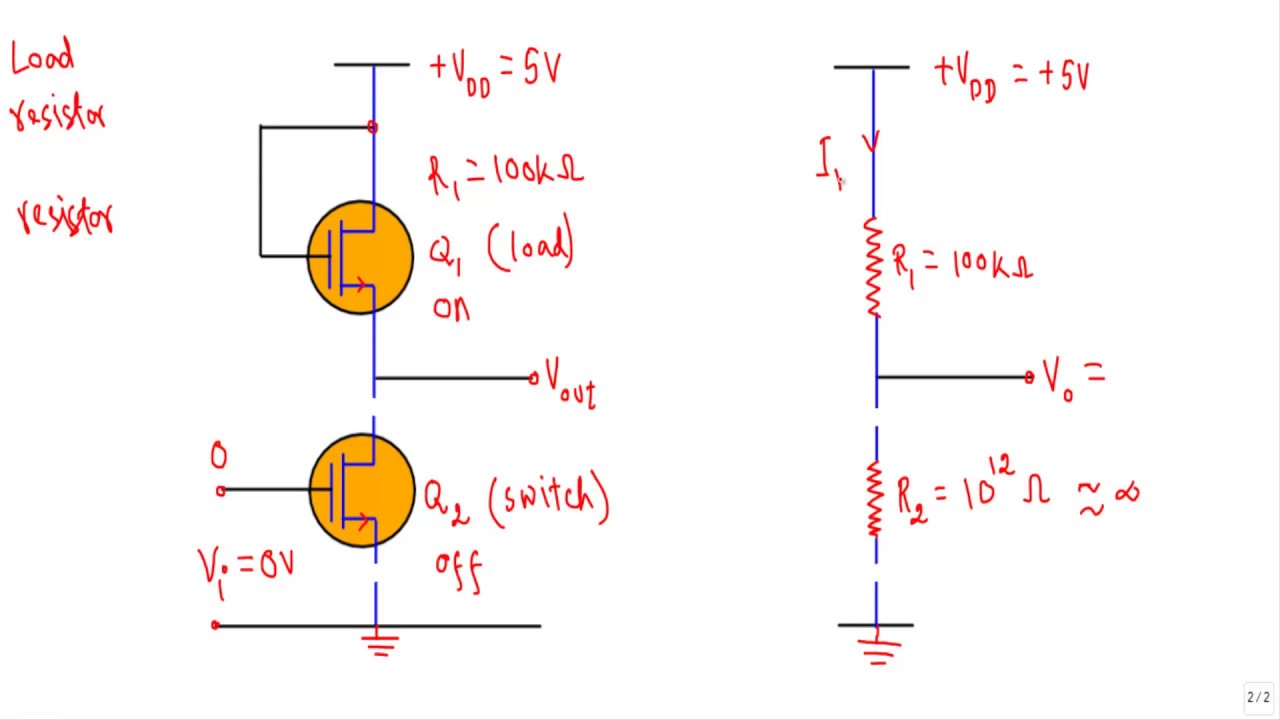

Cmos inverter circuit the nmos switch transmits the logic 0 level to the output, while the pmos switch transmits the logic 1 level to the output, depending. V_t0 = 0.8 v mu_n c_ox = 45.0 mu a/v^2 gamma = 0.38 v^1/2 |2 phi_f| = 0.6 v lambda = 0 v_dd = 5.0 v (a) calculate v_oh and v_ol values. Among the two mosfets, q 1 acts as the load mosfet, and q 2 acts as a switching mosfet. Now we note that it is an implementation of a simple inverter.

Both gates are short and if input =0 what is the output.??

In principle, the output voltage can range from 0 to v The inverter input voltage is v gs and the output is v ds. 1 with the channel lengths equal to 100nm, w m 1 = wn, w m 2 = k * wn, w m 3 = wn. Moving from nmos to pmos is the same as moving form npn to pnp.

Cmos scaling, vlsi bipolar transistor:

An alternative would be a cmos inverter with an nmos and a pmos. The syntax specifies the structure file name from the. In the nmos inverter, transistor t1 is used to replace mechanical switch a shown in fig. Nmos (off, saturation, ohmic) and putting the pieces together into a single characteristic.

Hi all if we replace the nmos in inverter with pmos what will be the output i.e top pmos source is given to 3.3v supply and its drain is connected to bottom pmos source and bottom pmos drain is ground.

The cmos inverter circuit is shown in. The first labeled an is to be simulated in atlas. In this video, i have explained nmos inverter and voltage transfer characteristics of nmos inverter with following timecodes: Transfer characteristics l14 cmos inverter (cont.) delay.

This cell will contain all the views related to this circuit.

The circuit netlist is written using standard spice syntax. We have seen the circuit at right while practicing our nmos skills. Transistor t2, which is of the depletion type, acts as the load resistor of t1, which is of the enhancement type. Note that the gate of t2 is shorted to its source, making vgs = 0.

The second is device parameter syntax.

• complementary mos (cmos) inverter analysis makes use of both nmos and pmos transistors in the same logic gate. Ni multisim live lets you create, share, collaborate, and discover circuits and electronics online with spice simulation included browser not supported safari version 15 and newer is not supported. Since the gate is always connected to the supply +v dd, the mosfet q 1 is always on. Remember to connect the bulks of the transistors.

A cmos inverter is a fet (field effect transistor), composed of a metal gate that lies on top of oxygen’s insulating layer on top of a semiconductor.

V max − v m nm l = v il − v ol = v m − − v min |a v(v m)| 1 v min nm h = v oh −v ih = v. A cmos inverter is an ingenious circuit, built form a pair of nmos and pmos transistors operating as complementary switches. Cmos inverter definition is a device that is used to generate logic functions is known as cmos inverter and is the essential component in all integrated circuits. These inverters are used in most electronic devices which are accountable.

(2) build the schematic from g.

The generalized circuit of an nmos inverter is shown in the figure below. Dray the nmos, turn the page upside down, change. The cmos inverter has the advantage of only drawing current when changing states. Generalized circuit for an nmos inverter from the above figure, we can see that the input voltage of the inverter is equal to the gate to source voltage of nmos transistor and output voltage of inverter is equal to drain to source voltage of nmos transistor.

Nmos inverter (1) create a cell named rec 2 nmos inv in virtuoso.

+ all static parameters of cmos inverters are superior to those of nmos inverters + cmos is the most widely used digital circuit technology in.