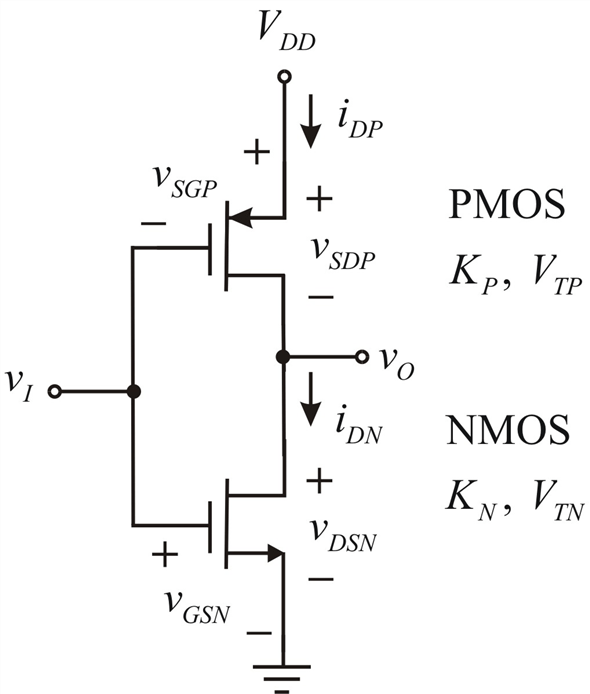

2.1 conventional cmos inverter the circuit diagram of a static cmos inverter is shown in fig. As you can see from figure 1, a cmos circuit is composed of two mosfets. The top of the cmos inverter is the pmos transistor, while the bottom transistor is nmos.

Solved Draw the circuit diagram of a CMOS inverter. Draw

A cmos inverter contains a pmos and a nmos transistor connected at the drain and gate terminals, a supply voltage vdd at the pmos source terminal, and a ground connected at the nmos source terminal, were vin is connected to the gate terminals and vout is connected to the drain terminals.(see diagram).

Specify the view type as schematic and click finish

Enter the cell name (e.g. 2) the pdn will consist of multiple inputs, therefore 6 11 cmos inverter circuit 12 cmos inverter circuit inversion (switching) threshold voltage For example, here is the schematic diagram for a cmos nand gate:

2(c )2 1 o p p r + c r = rp should match the input impedance of the cmos inverter.

To create a new schematic cell: 11/14/2004 cmos device structure.doc 4/4 jim stiles the univ. For example, if a crystal oscillator has the following parameters: If the cell does not exist, it is created.

The inverting nature of cmos logic circuits allows us to construct logic circuits for aoi and oai expressions using a structured approach aoi logic function implements the operations in the order and then or then not e.g., oai logic function implements the operations in the order or then and then not e.g., g(a,b,c,d ) a.b c.d

Use the pair of nmos and pmos gates on the right side of the ald1105 ic. The body effect is not present in either device since the body of each device is directly connected to the device’s source. In the cmos circuit, the two transistors like pnp & npn is connected to two supply rails like vdd & gnd. Cmos chips include a microprocessor, microcontrollers, memories like ram, and other digital logic circuits.

With input voltage vi = 0, the pmos will conduct and the nmos will remain off.

Both gates are connected to the input line. While a cmos inverter circuit serves as the basic logic gate to swap between those 2 voltage levels. Next, active (green) paths must be drawn for required transistors. Implementation determines the actual voltage.

3.43, we see that mos transistors t3 and t4 form the cmos inverter logic circuit.

Cmos inverter circuit the nmos switch transmits the logic 0 level to the output, while the pmos switch transmits the logic 1 level to the output, depending on the input signal polarity. When vin is high and equal to vdd, the nmos transistor is on, while the pmos is off. For a vdd of 3v, 5v, 7v, sketch the input waveforms required to test the functionality of the cmos inverter. Download scientific diagram | schematic of a cmos inverter circuit from publication:

Implementation determines the actual voltage.

Basic steps normally, the first step is to draw two parallel metal (blue) vdd and gnd rails. 1) the pun will consist of multiple inputs, therefore requires a circuit with multiple pmos transistors. The positive voltage of +vdd at the gate input of the nmos transistors will turn it on, while the same positive voltage at the gate input of the pmos transistor will keep it off. Demo_inverter) where you want a cell view to be created click file > new > view.

The principle of complementary symmetry was first introduced by george sziklai in 1953 who then discussed several complementary bipolar circuits.

Both are controlled by the same input. The cmos inverter is formed by connecting the pmos and nmos transistors in cascade, as shown below: There should be enough space between them for other circuit elements. Advances on cmos shift registers for digital data storage | the shift register is the heart of the current.

The top fet (mp) is a pmos type device while the bottom fet (mn) is an nmos type.

The create new view dialog box opens. Determine the vpp and dc offset setting required for function generator. Not surprisingly, the answer(s) to this question reveal a simplicity of design much like that of the cmos inverter over its ttl equivalent. The protection of these transistors can be done through resistors.

We find that t3 and t4 are driven separately from +vdd//vcc rail.